大功率电阻在VGA电路中为了获得满意的相位裕度PM,式23的分子必须大于分母。人们普遍认为PM = 60°足以维持放大器电路的稳定运行,当比值p2/GBW≈2时即可满足。关于PM,有一点很重要,它受到增益A1的负面影响,因此A1值很高会导致PM降低。另一方面,如果在高增益电平A1的情况下,VGA是稳定的,那么在低增益电平,也就是的情况下,VGA也会保持稳定。

大功率电阻在电源电压VDD为0.4 V时工作的电压比较器的拓扑结构。由于电压跨度非常有限,比较器必须能够处理铁轨到铁轨范围内的输入信号。关于电压比较器的另一个重要特性是迟滞。所提出的比较器拓扑结构包含四层迟滞,通过输入数字码可编程。额外的但非常受欢迎的功能,特别是在低功率电路是使能功能。其目的是抑制电路的功能,将内部电流消耗降低到漏电范围内。可以很容易地观察到所讨论的比较器拓扑结构的主要优点。与传统的三个MOS晶体管堆叠的比较器电路不同,这个提议的比较器只使用两个堆叠的器件,显然可以在较低的供电电压水平下工作。

大功率电阻设计VGA电路第二个好处是,一个差分结构可以实现轨到轨的输入电压范围,而不是两个单独的PMOS和NMOS放大器并行组合。另一个重要的贡献,如果比较传统比较器,是基于缺乏内部偏差参考块。这一特性简化并加快了设计过程,降低了总体静态电流消耗,并允许通过各自晶体管大小的电路支路设置电流。电路的模拟核心以及器件的尺寸。让讨论一下特低压轨对轨电压比较器的拓扑结构。可以看到,输入信号是由大块驱动的MOS晶体管处理的。大功率电阻这是一种解决各自器件阈值电压问题的好方法。与相当奇特的体积驱动电路有关的最可怕的问题是所谓的闭锁效应,它会导致电力供应轨之间的灾难性短路。但当电源电压设置为VDD = 0.4 V时,则不会发生这种情况,因为即使在T = 150℃时,PN结的阈值电压也不会下降到规定的值以下。

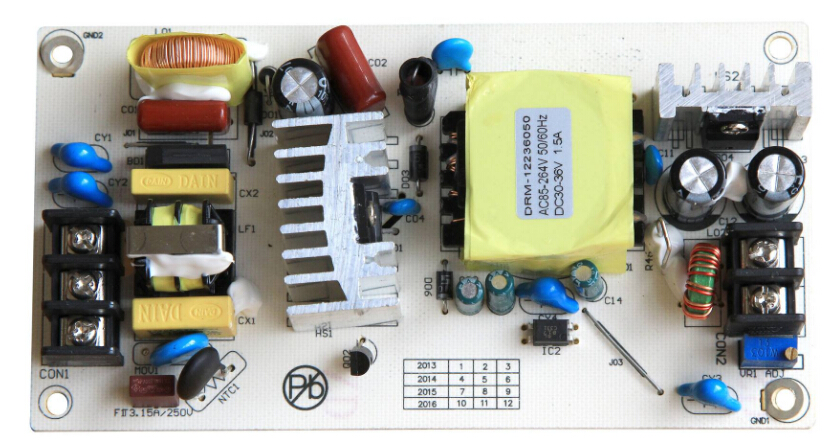

图12。