内建SAR ADC助力微控制器拓展新应用

使用分立ADC的应用,包括电能计量,掌上型医疗设备,工业控制系统,电源管理系统,游戏机和仪器仪表等,低成本微控制器为其提供高性能模拟功能逐渐成为可能。不过,在如此因为在满足频率和延迟需求的同时还要实现低成本和低功耗目标太难。

对于之前使用分立ADC的应用,包括电能计量,掌上型医疗设备,工业控制系统,电源管理系统,游戏机和仪器仪表等,低成本微控制器(MCU)为其提供高性能模拟功能逐渐成为可能。在通用控制系统应用中,往往需要奈奎斯特(奈奎斯特)ADC兼具低延迟,高频宽和低功耗特性,与此同时,其精准度达到约14位元有效位数(14位元ENOB ),价格也为大众所接受。在如此繁多的需求之下,目前的大多数SAR和Σ-Δ(DS)ADC都将惨遭淘汰,因为在满足频率和延迟需求的同时还要实现低成本和低功耗目标太难。

CDAC单元的元件数量会呈线性增加,但这些元件的匹配要求会导致平方律区域增大。为了限制元件总数,通常使用桥接或缩放元件来将DAC拆分成更小的子DAC。这些缩放元件并非单位规格,其寄生效应可能会导致进一步的不匹配和错误。通常由于区域限制,匹配超过10〜11位元对于微控制器整合是不可行的。因此,必须对ADC DAC元件执行某种形式的校准才能满足更高的解析度和精准度要求。

ADC架构

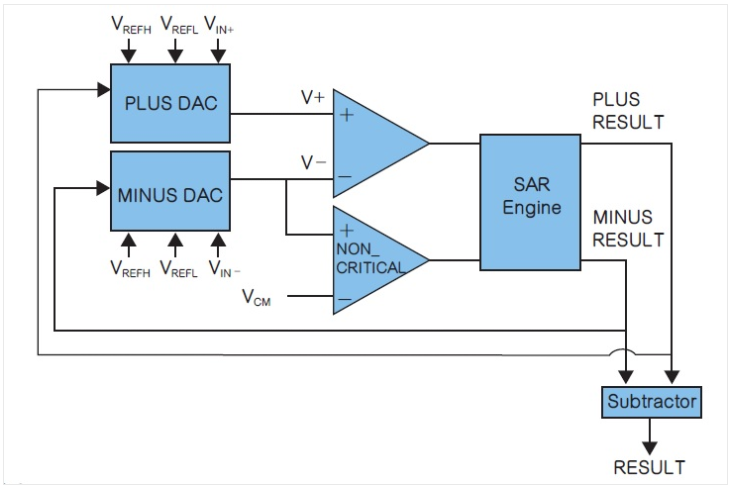

ADC架构,不包括通道多工器.SAR ADC通常由DAC和比较器构成反馈回路,并配有包括逐次逼近寄存器的逻辑.DAC通常由一组二进位加权元件组成,在本例中使用的是电容,一些应用中通常需要能够对极性未知的差分输入讯号进行转换,转换差分讯号也有助于透过共模杂讯抑制来提高结果的精准度。

实现差分ADC常面临诸多限制因素,其中一个是需要在逐次逼近期间将比较器的输入保持在其共模范围内。当比较器在共模电压下自动调零后,如果输入偏离该共模电压,将导致转换结果出现错误,进而增加非线性度。为了防止这一问题,我们添加了一个尺寸更小,功耗更低的「非关键」比较器。该比较器搭配负端DAC(负责采样VIN-)实现部分逐次逼近。这样可使比较器负输入V-足够接近VCM,从而确保比较器的精准度在1LSB以内。负端所需的逼近次数由比较器的共模抑制比(CMRR)和ADC的解析度决定.CMRR越高,所需的逼近次数越少。例如,如果12位元ADC中比较器的共模抑制比为66分贝,则只需在负端进行2次逼近(12位元LSB的二分之一=78分贝,因此负端逼近需将| VCMV- |电压减到12分贝)。

华助会阵列

CDAC是SAR中最重要的组成部分.SAR ADC的线性度取决于电容阵列中的电容匹配,分离电容结构是限制晶片面积的常用方法。图2所示的CDAC拓扑结构结合校准提供了一种可在电容阵列大小(96个电容),速度,杂讯和线性度之间取得最佳权衡的设计。每个电容代表一组单位电容,透过对最高有效位元电容进行校准,可以缩小单位电容的尺寸。

ADC校准

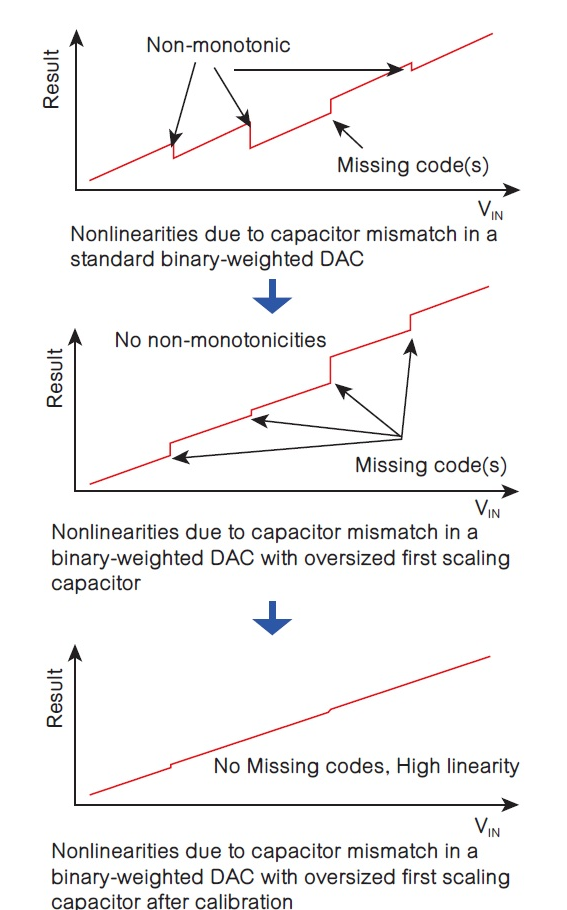

SAR ADC有许多种校准方法,一些方法使用基于数位关联的校准,另一些方法使DAC相关技术测量DAC中的电容比例差,然后透过类比调整方式来修改DAC元件或者通过数位调整方式来调整结果。中ADC使用的测量方法,是透过测量电容比例差来确定电容误差值,然后透过数位调整方式来修改结果。正端和负端华助会的MSB电容均被校准。为了在调整SAR结果后不产生较大的非线性度,校准前的CDAC必须是单调的,将缩放电容CSC1(图3)的尺寸调整为略大于理想值可以保证单调性。

为了确定校准误差值,每个MSB电容(由位元15:11控制)都将与所有最低有效位元电容的组合进行比较。例如,校准的某一步是将位元11电容(1C)与位元10:0电容和末位元电容(由于CSC1过大而略大于1C)进行比较下一步是将位元12电容(2C)与位元11:0电容和端接电容(略大于2C)进行比较。依此类推,每个MSB电容都会执行这一过程,校准系数会进行累加并储存在记忆体中,每个ADC需要的储存空间不到128位元。完成正常ADC转换之后,从未经校准的结果中减去对应于MSB结果的校准值可获得校准结果。

实验结果

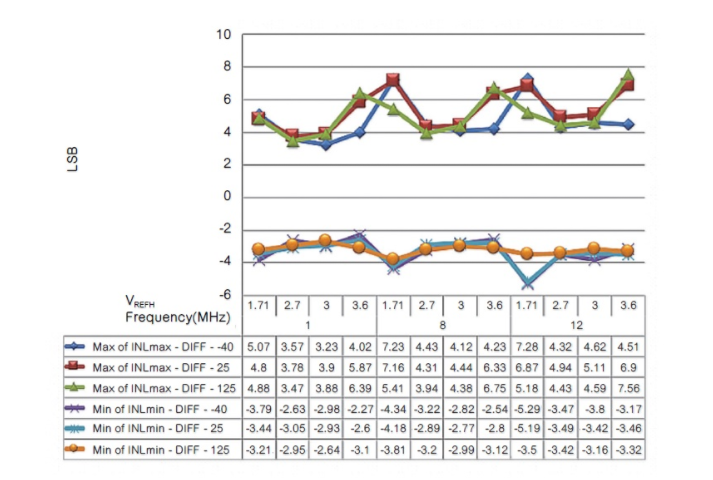

ADC采用90nm CMOS制程制造,ADC电路已整合到90nm微控制器中,目前处于生产阶段。在某晶圆生产批次中随机选取了4个元件,测得的ADC积分非线性(INL)误差如图5所示图中所示的最小和最大INL的测试条件为:最大转换速率,时脉频率从1MHz的12MHz的〜(最大时脉频率),电压从1.71V〜3.6V,温度从-40 ℃〜125℃。

结论

借助90nm CMOS技术,现已成功使用金属边缘电容实现了一个低功耗差分自校准460kS / s16位元轨到轨输入SARA / D转换器。这款ADC在全速下测得的电流消耗为800mA,适于多种应用。矽测量显示其总体性能达13.5〜14.5ENOB,该电路现已整合到90纳米微控制器中,目前处于生产阶段。

最新资讯

- SMS-R025-1.0电阻,精密伊萨贴片电阻器,,,

- 低噪声电阻器在扬声器产品非常重要,,,

- SMD贴片电阻器无需在安装前在板上钻孔,,,

- SMD电阻器和电容器专为表面贴装设计的,,,

- SMD电阻器使用激光束对电阻值进行微调,,,

- 贴片电阻器采用字母数字标记电阻器,,,

- 串联电阻器和分压器在电子电路中作用,,,

- 固定电阻器和可变电阻器最大的区别,,,

- 合金电阻器抵抗电流的电子部件与哪些,,,

- 如何选择电阻器的额定功率?,,,

- 低瓦数电阻器和高功率电阻有什么区别,,,

- 分流电阻器被应用在高频噪声困扰的电,,,

- 高功率电阻器热能耗散是用功率来衡量,,,

- 金属箔电阻器应用直流和脉冲电流电,,,

- 可变电阻器适用于所有类型的电阻器,,,

热销电阻

公司新闻

- 全球MICROHM客户隐私权更新通知,,,

- 万利隆将参加日本2018汽车电子技术展,,,

- 2018年电阻打响了涨价的第一枪,那么,,,

- 贴片电阻最重要的五种基本参数,,,

- 万利隆电子将参加2018德国慕尼黑电子,,,

- 万利隆参展日本2018汽车电子技术展,,,

- MICROHM集团出席第十八届韩国·香港商务,,,

- 精密电阻涨价了,为什么2018年电阻市,,,

- 精密电阻器在风力发电系统平台的应用,,,

- 0Ω电阻是什么电阻又该如何使用0Ω电阻,,,

- 半导体行业增长趋缓电阻器是否有增长,,,

- 汽车分流电阻shunt应用于新能源汽车电,,,

- 精密采样电阻采样精度影响,精密采样,,,

- 1M至50M电阻值,选精密薄膜电阻还是精密,,,

- 精密电阻助力于可再生能源中太阳能发,,,